# Интерфейсный блок Ethernet MAC 10/100/1G

Ethernet — стандарт передачи данных в режиме полного или полудуплекса для построения локальных сетей или соединения «точка-точка».

MAC (англ. Media Access Control) - уровень протокола Ethernet в соответствии со стандартом IEEE 802.3.

# Общее описание

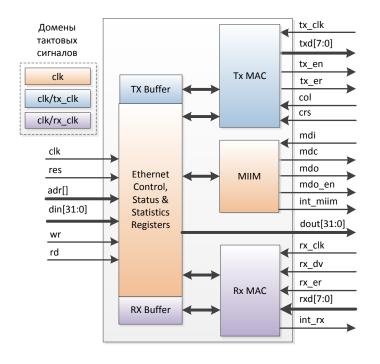

Ethernet MAC 10/100/1G является контроллером MAC уровня стандарта Ethernet. Он имеет интерфейсы (G)MII к устройству PHY уровня с одной стороны и 32-разрядный generic пользовательский интерфейс с другой. Поддерживаются номинальные скорости передачи 10, 100 и 1000 Мбит/с.

Ethernet MAC 10/100/1G пересылает кадры, записанные пользователем в буфер, и принимает кадры через интерфейс (G) MII. В режиме полудуплекса проводится обработка коллизий согласно алгоритму CSMA/CD.

Модуль имеет 3 независимых домена тактовых частот (интерфейс пользователя, частота приемника Ethernet 2,5/25/125 МГц, частота передатчика Ethernet 2,5/25/125 МГц) передача данных между которыми осуществляется с помощью схем синхронизации и защиты от метастабильности.

# Поддержка

- Техническая консультация в течение 90 дней

- Настройка под нужды Заказчика

- Дополнительная техническая поддержка

- Комплексные услуги по интеграции IP блоков

#### Комплект поставки

- RTL модель на языке Verilog

- Verification IP на SystemVerilog

- Approximately Timed TLM модель

- Функциональная модель для верификации

- Комплект документации на русском языке

- ПО для конфигурирования

## Функциональные возможности

- Динамическая настройка номинальной скорость обмена через (G)MII Ethernet — 10, 100 и 1000 Мбит/с

- Динамическая настройка режима передачи полный дуплекс или полудуплекс Ethernet

- Опциональные регистры статистики сетевого интерфейса

- 32-битный Generic интерфейс пользователя

- Программируемый МАС адрес

- Генерация и проверка CRC-32

- Повторная передача при возникновении коллизий

- Буферы для приемника и передатчика с конфигурируемым размером (1, 2, 4, 8, 16, 32, 64, 128 КБ)

- Интерфейс МІІМ для конфигурирования устройств РНҮ

## Характеристики и параметры

Блок синтезировался на различных библиотеках ПЛИС и СБИС. Синтез схемы с буферами размером по 32 Кбайт дал следующие результаты:

|                                      | Fmax, МГц        | LUT/ALUT                        | Регистры | ОЗУ, бит  |

|--------------------------------------|------------------|---------------------------------|----------|-----------|

| Xilinx Virtex6 (XC6VLX240T-1FFG1156) | 125 <sup>*</sup> | 5154                            | 3291     | 524288*** |

| Altera StratixII (EP2S130F1508C5)    | 134*             | 5790                            | 3340     | 524288    |

| Generic ASIC 90 nm                   | 182              | 41168/<br>1408117 <sup>**</sup> | 3400     | 524288    |

<sup>-</sup> частота рассчитывалась для максимальной температуры, минимального значения напряжения для данной библиотеки;

www.scanru.ru

web:

<sup>\*\* -</sup> площадь выражена числом эквивалентных вентилей NAND2 с минимальной для данной технологии площадью без учета блоков памяти / с учетом блоков памяти.

<sup>\*\*\* -</sup> размер ОЗУ без учета бит четности .