# Интерфейсный блок UART

UART (англ. Universal Asynchronous Receiver Transmitter) — последовательный асинхронный стандарт передачи данных в режиме полного дуплекса для простого и недорогого соединения «точка-точка» микроконтроллеров, микропроцессоров и различных периферийных устройств.

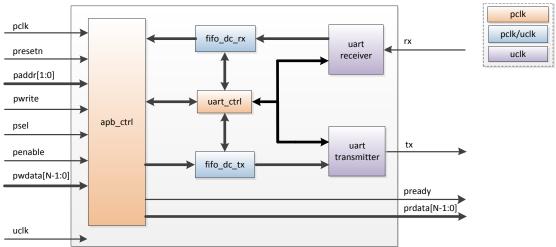

#### Общее описание

Блок имеет интерфейсы APB3 или Generic со стороны пользователя с различной шириной шины данных (8, 16 или 32 бит). Для подбора точной частоты передачи через интерфейс UART используется опорная тактовая частота UCLK. С ее помощью можно организовать передачу данных со стандартными для интерфейса скоростями (2400, 4800, 9600, 19.2к, 38.4к, 57.6к, 115.2к...) независимо от наличия и значения частоты со стороны пользователя. Частоты интерфейсов APB/Generic и UART могут быть независимы друг от друга, передача данных между ними осуществляется за счет встроенных схем синхронизации, защиты от метастабильности и буферов FIFO. Если используется общая частота для UART и APB/Generic, то нет необходимость в схемах синхронизации и ресурсы для реализации схемы могут быть сокращены.

Передача и прием данных осуществляются последовательно по выделенной линии в соответствии с заданной конфигурацией. Приемник и передатчик могут работать одновременно и независимо друг от друга.

## Функциональные возможности

- одновременные прием и передача по UART

- динамически настраиваемая длина байта (5, 6, 7 или 8 бит) с опциональным битом четности

- пользовательский интерфейс ведомого на шине APB или интерфейс Generic с конфигурируемой шириной интерфейса (8, 16 или 32 бит)

- буферы для приемника и передатчика (на регистрах или двухпортовом ОЗУ) с конфигурируемым размером до 128 Б

- синхронная схема с 2 независимыми тактовыми доменами для интерфейсов UART и APB с конфигурируемой схемой синхронизации и защиты от метастабильности

- скорость передачи до 1/4 частоты UCLK

#### Поддержка

- Техническая консультация в течение 90 дней

- Настройка под нужды Заказчика

- Дополнительная техническая поддержка

- Комплексные услуги по интеграции IP блоков

#### Комплект поставки

- RTL модель на языке Verilog

- Функциональная модель для верификации

- Комплект документации на русском языке

- ПО для конфигурирования

### Характеристики и параметры

Блок синтезировался на различных библиотеках ПЛИС и СБИС. Синтез схемы с 32-битным интерфейсом АРВ и буферами размером по 128 байт дал следующие результаты:

|                                   | Fmax <sup>*</sup> , МГц | LUT/ALUT | Регистры | ОЗУ, бит |

|-----------------------------------|-------------------------|----------|----------|----------|

| Xilinx Virtex5 (XC5VLX30-3FF324)  | 322                     | 280      | 189      | 2048     |

| Altera StratixII (EP2S60F672C5ES) | 110                     | 935      | 2206     | -        |

| Generic ASIC 90 nm                | 100                     | 21061**  | 2238     | -        |

<sup>🔭 -</sup> частота рассчитывалась для максимальной температуры, минимального значения напряжения для данной библиотеки;

<sup>˜ -</sup> площадь выражена числом эквивалентных вентилей NAND2 с минимальной для данной технологии площадью.